このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

Simulink でのシングル レート信号の整列

この例では、ランダムな信号 sig1 と信号の遅延コピー sig2 の間の遅延をFind Delayブロックを使用して計算します。Delay (Simulink)ブロックのインスタンスを使用して信号の遅延と整列を行います。

モデルの構造

このモデルは、並列信号パスを使用して、信号 sig1 と信号 sig2 間の遅延のサンプル数を計算および比較します。

上のパスでは、

Find Delayブロックを使用してsig1とsig2の間の遅延を計算します。上のパスのDelayブロックは、計算された信号遅延を入力し、その遅延を基準信号sig1に追加します。下のパスでは、

Delayブロックを使用して固定の遅延を基準信号に追加します。固定の遅延がある信号と計算された遅延がある信号を比較して、両方の信号に同じ遅延が適用されたことを示します。

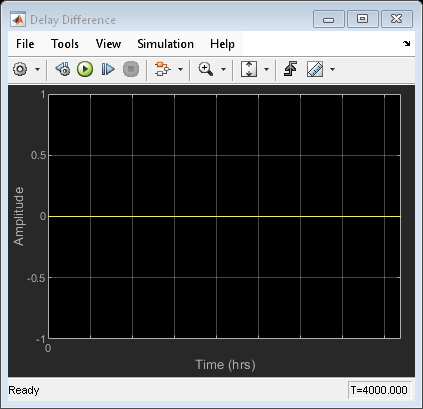

遅延信号の比較

下の遅延パスと上の遅延パスで出力された信号間の差分をプロットします。プロットされた遅延の差分がゼロの場合、両方の信号に同じ遅延が適用されていることを示します。計算された遅延はシミュレーションの実行後に表示されます。

The delay computed by the |Find Delay| block is 7.