エンジニアリング チームは、MATLAB および Simulink を使用したモデルベースデザイン (MBD、モデルベース開発) により、複雑な組み込みシステムを設計して量産品質の C、C++、および HDL コードを生成しています。MathWorks のツールは、シミュレーション テストと形式的手法に基づく静的解析を使用して、厳密さと自動化によりモデルベースデザインを補完し、エラーを早期に発見して高品質を実現します。

MATLAB と Simulink を使用すると、次のことが可能になります。

MATLAB および Simulink を使用した検証と妥当性確認

要件の検証

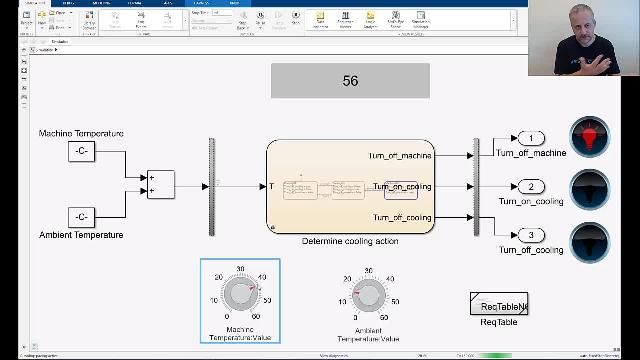

ドキュメント、スプレッドシート、または IBM Rational DOORS などの要件管理ツールに保存できる非形式的なテキスト要件から、開発プロセスを開始します。Requirements Toolbox を使用すると、要件をアーキテクチャ、設計、生成コード、およびテスト アーティファクトとともにインポート、表示、作成、管理することができます。要件から System Composer、Simulink、Stateflow での設計、または Simulink Test でのテストまでのデジタルスレッドを作成することができます。このトレーサビリティにより、実装またはテストのギャップを特定し、変更が設計やテストに及ぼす影響を迅速に把握することができます。

Requirements Toolbox の Requirements Table ブロックを使用して、要件を形式化し、一貫性、完全性、正確性を解析して早期に妥当性を確認することができます。Simulink Test の時間的評価では、評価およびデバッグできる自然言語形式の正確なセマンティクスで評価を指定することにより、テキスト要件を検証することができます。

Simulink による体系的な故障注入および FMEA

シミュレーションを使用して故障およびその他の異常動作の影響を解析し、安全要件の開発やシステムのロバスト性検証を行えます。Simulink Fault Analyzer では、シミュレーションを使用して故障の影響と安全性を体系的に解析できます。この製品は、設計を変更することなく、故障注入シミュレーションを実行します。Simulink、Simscape、および System Composer でモデル化した故障を管理できます。シミュレーション データ インスペクターを使用して、故障の影響を解析できます。[複数のシミュレーション] パネルを使用して、故障感度解析を実施できます。シミュレーションを活用しながら、故障モード影響解析 (Failure Mode and Effects Analysis: FMEA) などの安全解析を実行できます。Simulink Fault Analyzer を使用すると、故障、ハザード、故障検出と故障緩和のロジック、その他のアーティファクトの間の形式的な関係性を作成できます (Requirements Toolbox を使用)。

関連情報

- Simulink Fault Analyzer の基礎、パート 2: Simulink Fault Analyzer による故障の定義とモデル化 (9:13)

- Simulink Fault Analyzer の基礎、パート 3: 安全性解析マネージャーでのスプレッドシートの作成 (5:25)

- Simulink Fault Analyzer の基礎、パート 4: 故障感度解析の実施 (5:23)

- Simulink Fault Analyzer の基礎、パート 5: フォールトトレラントな燃料制御システムの故障解析 (7:53)

- Simulink Fault Analyzer の基礎、パート 6: 航空機の昇降舵制御システムの故障解析 (9:05)

認証規格への準拠

DO-178、ISO 26262、IEC 61508、IEC 62304、および MathWorks Advisory Board (MAB) スタイルガイドラインなどの規格に合わせて、モデルとコードの検証を自動化します。Simulink Check は、開発中に規格およびガイドラインに対する違反を特定するための、業界認定のチェックやメトリクスを提供します。独自の規格やガイドラインに合わせてカスタムチェックを作成できます。IEC Certification Kit (for ISO 26262 and IEC 61508) および DO Qualification Kit (for DO-178 and DO-254) には、コード生成製品および検証製品の適格性を確認し、組み込みシステムの認定の合理化に役立つ、ツール適格性確認アーティファクト、証明書、およびテストスイートが用意されています。

エラーがないことの証明および要件の形式的検証

形式的検証では、設計をシミュレーションすることなく、整数オーバーフロー、デッドロジック、配列アクセス違反、およびゼロ除算を引き起こす潜在的な設計エラーを検出します。Simulink Design Verifier では、設計にエラーやセキュリティの脆弱性がないことを形式的に検証できます。また、Simulink Design Verifier では、設計が重要な要件を満たしていることを証明できます。ツールが例外を検出すると、デバッグ用の反例を生成します。

テストの自動生成

テストのギャップ、意図しない機能、要件エラーの特定は重要です。Simulink Coverage は、テスト中に実行されるモデルまたは生成コードのカバレッジを測定します。条件、判定、改良条件判定カバレッジ (MCDC)、およびカスタムのカバレッジ オブジェクティブなどの業界標準メトリクスを適用します。Simulink Design Verifier では、テストケースを自動的に生成して不完全なカバレッジに対処し、構造的および機能的なカバレッジ オブジェクティブを達成できます。

静的コード解析

手書きのコードおよび生成されたコードの検証のために、Polyspace 製品は形式的手法を使用してバグを検出し、重大なランタイムエラーがないことを証明します。テストケースやコード実行は必要ありません。Polyspace Bug Finder は、MISRA、ISO 26262、IEC 61508、DO-178、および FDA 規制などの規格への準拠を確認し、文書化します。ソフトウェアのセキュリティ脆弱性と CWE、CERT-C、ISO/IEC 17961 などの規格について確認できます。Polyspace Code Prover は、静的解析を実施して、C および C++ ソースコードのオーバーフロー、ゼロ除算、範囲外の配列アクセス、およびその他のランタイムエラーがないことを証明します。