Filter Design HDL Coder は、MATLAB で設計した固定小数点フィルターを実装するための、FPGAまたはASIC向けの合成可能で移植可能な VHDL® コードと Verilog® コードを生成します。また、生成されたコードをシミュレーション、テスト、検証するための VHDL および Verilog のテストベンチを自動的に作成します。

詳細を見る:

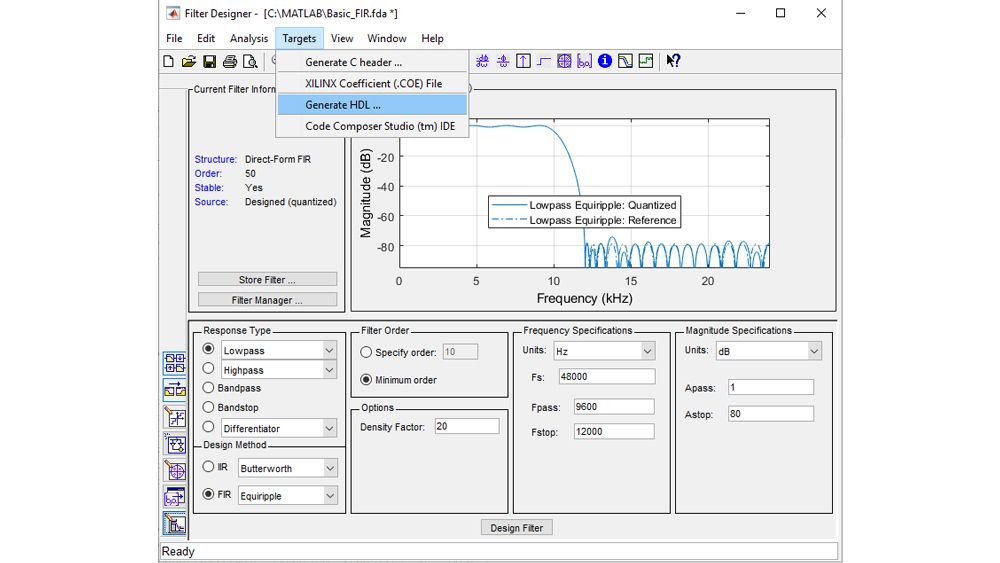

Filter Design HDL Coder は DSP System Toolbox と統合されており、設計と実装のための統一された環境を提供します。フィルターの設計と VHDL コードおよび Verilog コードの生成は、MATLAB コマンドラインから、または DSP System Toolbox で、フィルターデザイナー アプリまたは Filter Builder アプリを使用して実行できます。

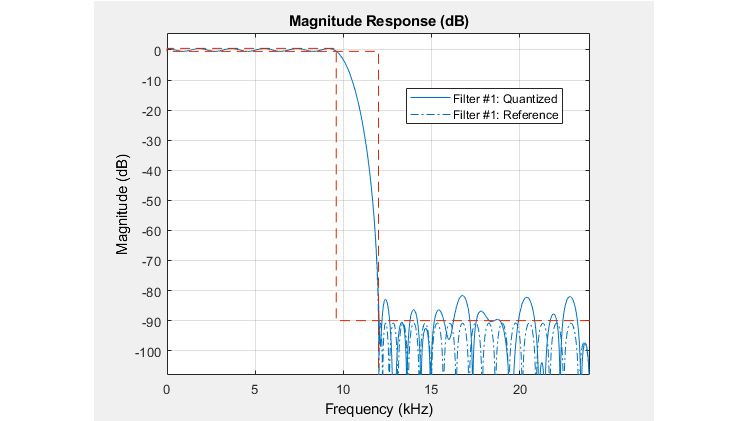

Filter Design HDL Coder への設計エントリ入力は、以下の 2 つの方法のいずれかで作成する、量子化されたフィルターです。

- フィルターを DSP System Toolbox で設計および量子化する

- フィルターを Signal Processing Toolbox で設計し、DSP System Toolbox で量子化する

Filter Design HDL Coder では、以下のようないくつかの重要なフィルター構造がサポートされています。

離散時間有限インパルス応答 (FIR)。これには、対称、非対称、および転置構造が含まれます。

2 次セクション型 (SOS) 有限インパルス応答 (IIR)。これには、直接型 I、直接型 II、および転置構造が含まれます。

マルチレート フィルター。これには、カスケード積分櫛形 (CIC) インターポレーターおよびデシメーター、直接型 FIR および転置 FIR ポリフェーズ内挿およびデシメーター、FIR ホールドおよび線形内挿、FIR ポリフェーズ サンプル レート変換構造が含まれます。

非整数遅延フィルター。これには Farrow 構造が含まれます。

Filter Design HDL Coder は、カスケード接続された マルチレートおよび離散時間フィルターから HDL コードを生成できます。これらのシングルレート フィルター構造およびマルチレート フィルター構造では、固定小数点および浮動小数点 (倍精度) の実現がサポートされます。さらに、FIR 構造では、符号なし固定小数点係数がサポートされます。

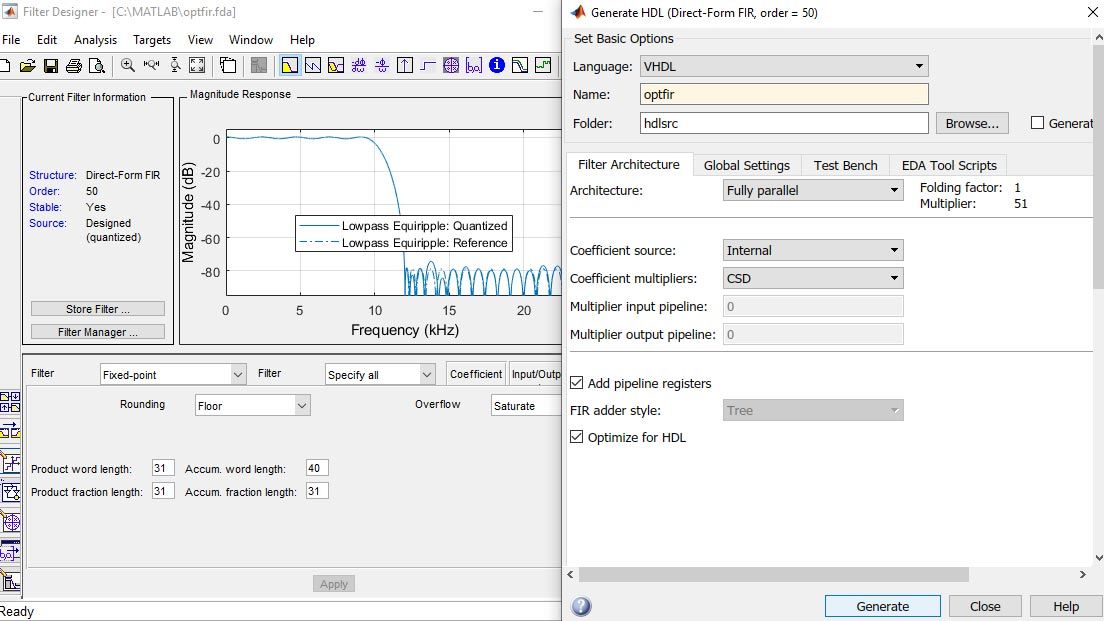

フィルターデザイナー アプリまたは Filter Builder アプリから、固定小数点フィルターの VHDL コードまたは Verilog コードを生成できます。どちらのアプリでも、HDL コードを生成する際に、実装アーキテクチャの指定、ポートデータタイプの選択、パイプラインレジスタの挿入などの HDL 生成オプションを設定できます。その他のオプションでは、フィルター HDL 設計のテストベンチを生成および設定できます。

Filter Design HDL Coder は、オプション設定またはプロパティ名とプロパティ値のペアに基づいて、フィルターを設定し、量子化フィルターのテストベンチ HDL コードを生成します。これらの設定により、次のことが可能になります。

- 言語要素の指定

- ポートパラメーターの指定

- 高度な HDL コード機能の使用

すべてのプロパティにはデフォルト設定があります。フィルター設計と解析アプリまたは Filter Builder アプリで設定を調整すると、HDL 出力をカスタマイズできます。このアプリでは、以下に関連するプロパティを設定できます。

- HDL 言語設定

- ファイル名およびフォルダー設定

- リセット仕様

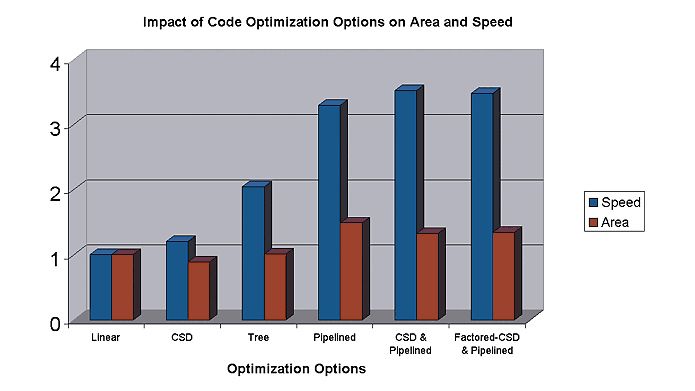

- HDL コードの最適化

- テストベンチのカスタマイズ

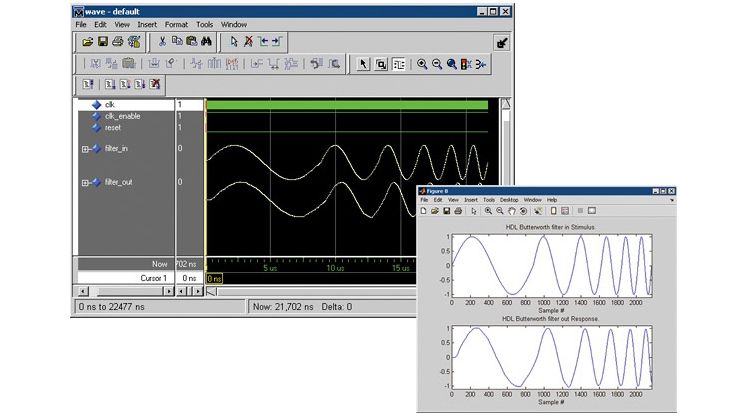

VHDL または Verilog のテストベンチを生成して、生成された HDL コードをシミュレートおよびテストできます。さらに、HDL Verifier を使用すれば、Simulink コシミュレーション ブロックを生成して、Simulink で動作するビヘイビア フィルター モデルとテストを、Cadence® Incisive® および Xcelium™ シミュレーター、または Mentor® ModelSim® および Questa® シミュレーターで動作する、生成された HDL に接続できます。コシミュレーションにより、生成された HDL コードからの結果と Simulink で動作するビヘイビア フィルター モデルからの結果を直接比較できるため、フィルター設計の検証が簡単になります。この統合により、MATLAB および Simulink の高度な分析および可視化機能を適用して、フィルター設計の HDL 実装をテスト、デバッグ、検証できます。