このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

Simulink での GSM デジタル ダウン コンバーター

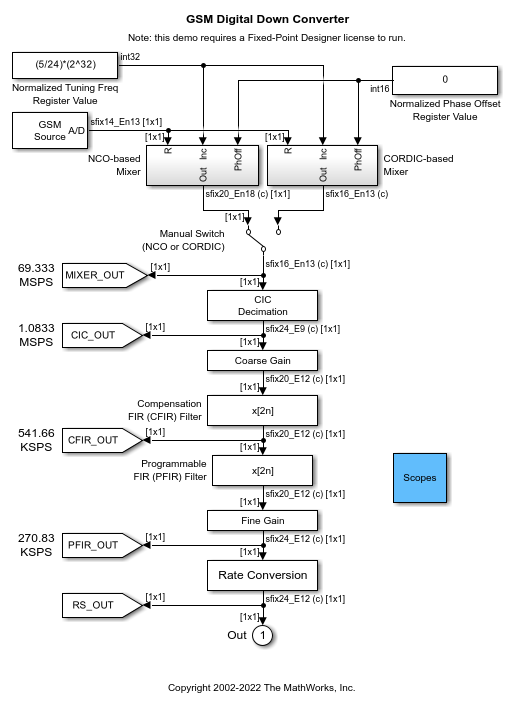

この例では、GSM (Global System for Mobile) ベースバンド変換における固定小数点デジタル ダウンコンバーターの定常状態の動作をシミュレーションする方法を説明します。モデル例では、Simulink® および DSP System Toolbox™ のブロックを使用して、TI GC4016 Quad デジタル ダウン コンバーター (DDC) の動作をエミュレートします。

DDC は以下の操作を実行します。

入力信号のデジタル ミキシング (ダウン コンバージョン)

狭帯域のローパス フィルター処理と間引き

データ ストリームのゲイン調整と最終リサンプリング

このモデルでは、DDC には高いサンプルレート (69.333 MSPS) のバンドパス信号が入力されます。DDC は、復調に備えて低サンプルレート (270.83 KSPS) のベースバンド信号を生成します。

GSM ソースの変更

モデル例の GSM Source ブロックを使用して、チャープ信号と正弦波信号を切り替えることができます。このブロックを別のソースに置き換えてアプリケーションをモデル化することはできますが、ダウンストリーム混合器サブシステムのパラメーターを調整する必要があります。

正規化されたチューニング周波数および位相オフセット値の調整

GSM ソース信号が受信され、エラーを最小限に抑えながらミックス ダウンされるかを確認するには、Normalized Tuning Freq Register Value および Normalized Phase Offset Register Value を調整します。

この例では TI GC4016 Quad デジタル周波数変換器をシミュレーションしているため、これらの値は特定の形式で入力しなければなりません。Normalized Tuning Freq Register Value は、32 ビットの 符号付き 2 の補数整数で、0 からサンプリング周波数までの正規化された範囲を表さなければなりません。ダウン コンバージョンには正の周波数値を使用します。Normalized Phase Offset Register Value は、16 ビットの符号なしの整数で、正規化された範囲を表さなければなりません。詳細については、TI GC4016 Quad デジタル周波数変換器のドキュメンテーション、および DSP System Toolbox NCO ライブラリ ブロックのリファレンス ドキュメンテーションを参照してください。

NCO ベースと CORDIC ベースの混合器実装の比較

Digital Mixer Real Output スコープと Mixer Output Comparison スコープを表示して、NCO ベースの混合器実装出力を CORDIC ベースの混合器実装出力と比較します。どちらの実装も同じような出力値を生成するように作成できますが、実装の選択は、使用可能なハードウェア リソースとパフォーマンス制約に基づきます。通常、NCO ベース手法は、ルックアップ テーブル サイズ (読み取り専用メモリ リソース) を速度パフォーマンスと交換し、CORDIC ベース手法は必要な CORDIC カーネル反復数に基づいて速度パフォーマンスをより小さいメモリ リソースと交換します。

NCO ベースの混合器パラメーターの調整

NCO Cosine Spectrum Analyzer ブロックの出力で、NCO-based Mixer サブシステム ブロック パラメーターを調整した効果を確認できます。

ディザリング

利用できる帯域幅全体にスプリアス周波数を広げるには、ディザー信号を加算器の位相値に追加します。この例では、2 進数のシフト レジスタと排他的論理ゲート (NCO ブロック内部) で構成される PN シーケンス発生器によってディザー信号が生成されます。ディザーのビット数は以下で自動的に決定されます。

number of dither bits = accumulator word length - table address word length

ディザーのビット数が最適値を超えると、ノイズ フロアのレベルが上昇し始めます。ディザーのビット数が減少し最適値を下回ると、現れるスプリアス周波数によって、NCO システムのスプリアス フリー ダイナミック レンジが減少します。

詳細については、DSP System Toolbox NCO ライブラリ ブロック リファレンス ドキュメンテーションを参照してください。

CORDIC ベースの混合器パラメーターの調整

CORDIC Cosine Spectrum Analyzer ブロックの出力で、CORDIC-based Mixer サブシステム ブロック パラメーターを調整した効果を確認できます。

Phase Accumulator with Dither Generator

Phase Accumulator with Dither Generator サブシステムは、関数 CORDIC Complex Rotate の角度入力 Theta を計算します。CORDIC Cosine Spectrum Analyzer ブロックの出力で、Phase Accumulator with Dither Generator サブシステム パラメーターを調整した効果を確認できます。

上記の NCO ベース混合器の場合、利用できる帯域幅全体にスプリアス周波数を広げるには、ディザー信号を位相アキュムレータ値に追加します。ディザー信号は 2 進数のシフト レジスタと排他的論理ゲート (Phase Accumulator with Dither Generator 内部) で構成される PN シーケンス発生器によって生成されます。ディザー ビットの数は、NCO ベース混合器の余弦スペクトルのパフォーマンスと一致するように 15 になりました。

CORDIC Complex Rotate

CORDIC Complex Rotate は、CORDIC 回転アルゴリズムを使用して u * exp(j*theta) を計算します。関数 CORDICROTATE については、Fixed-Point Designer™ のドキュメンテーションを参照してください。CORDIC ベースのデジタル混合器手法に関する詳細については、下記のリファレンスも参照してください。

間引きフィルター パラメーターの調整

CIC Decimator、Compensation FIR、および Programmable FIR ブロックを一緒に使用すると、以下の項目を実現できます。

高い間引き率

エイリアシングの減衰

アプリケーション固有のフィルター処理

フィルター デザイナーを使用すれば、フィルターを可視化して解析できます。フィルター デザイナーの詳細については、Signal Processing Toolbox™ ドキュメンテーションを参照してください。

モデル例内の CIC Decimator ブロックをダブルクリックすると、フィルターの実装を確認できます。DDC をカスタマイズするには、CIC Decimation ブロック パラメーターを編集して CIC フィルターを変更します。

CIC Decimation フィルターは、カスケード接続積分器櫛形構造内の間引きフィルター処理を実行するために、整数オーバーフロー "wrap" 演算を使用して実装されます。このフィルターのタイプは FPGA や ASIC などのハードウェアで実装する場合に効率的です。これは、必要な算術演算が加算のみで、乗算を必要としないためです。CIC フィルターの詳細については、下記のリファレンスを参照してください。

Compensation FIR (CFIR) Filter ブロックは CIC 通過帯域のロールオフに対する調整を行い、Programmable FIR (PFIR) Filter ブロックは GSM ベースバンド スペクトル マスクの条件を満たすために信号をフィルター処理します。これらのフィルターのゲインと係数は調整可能です。

Compensation FIR (CFIR) Filter に対する入力ゲインは、COARSE ゲイン パラメーターを使用して設定されます。TI GC4016 Quad デジタル周波数変換器では、2^COARSE に従って CIC フィルターの出力を 0 ~ 7 ビットだけシフトするには、COARSE パラメーターからの入力が必要です。したがって、Coarse Gain ブロック マスクの COARSE ゲイン パラメーターに対して 0 ~ 7 を入力します。

Programmable FIR(PFIR) Filter ブロックの出力時のゲインは、FINE ゲイン パラメーターを使用して設定されます。TI GC4016 Quad デジタル周波数変換器では、FINE/1024 に従って信号を 1 ~ 4 ビットだけシフトするには、FINE パラメーターからの入力が必要です。したがって、Fine Gain ブロック マスクの FINE ゲイン パラメーターに対して 1 ~ 16383 を入力します。

Rate Conversion ブロック パラメーターの調整

この DDC の最終ステージでは、特定のシステムの復調器入力のベースバンド周波数に一致するように、DDC の出力レートを変更できます。Rate Conversion ブロックは、DSP System Toolbox の FIR Rate Conversion ブロックと同じように動作する固定小数点フィルターです。Rate Conversion ブロックの NDELAY パラメーターは内挿係数で、NDEC パラメーターは間引き係数です。

DDC の解析

シミュレーションの結果を観測して解析するには、スコープと固定小数点ツールを使用できます。

スコープ

モデル例の Scopes ブロックをダブルクリックすると、次のスコープにアクセスできます。

NCO コサイン スペクトル

CORDIC コサイン スペクトル

デジタル混合器の実数出力

混合器出力の比較

CIC 間引き出力

補償 FIR フィルター

プログラム可能な FIR フィルター

リサンプル出力

固定小数点ツール

例に対して固定小数点ツールのインターフェイスを呼び出すには、[解析] メニューの [固定小数点ツール] を選択します。このインターフェイスを使用すると、モデル例の任意のサブシステムにある固定小数点ブロックの最大値、最小値およびオーバーフローを表示できます。固定小数点ツールの詳細については、Simulink および Fixed-Point Designer™ のドキュメンテーションを参照してください。

参照

[1] Hogenauer, E. B., "An Economical Class of Digital Filters for Decimation and Interpolation," IEEE® Transactions on Acoustics, Speech, and Signal Processing, ASSP-29(2):155 - 162, 1981.

[2] Lohning, M., Hentschel, T., and Fettweis, G., "Digital Down Conversion in Software Radio Terminals", Proceedings of the Tenth European Signal Processing Conference (EUSIPCO), 1517 - 1520, 2000.

[3] Valss, J., Sansaloni, T., Perez-Pascual, A., Torres, V., and Almenar, V., "The Use of CORDIC in Software Defined Radios: A Tutorial", IEEE Communications Magazine, 46 - 50, September 2006.

[4] Yang, S., Wu, Z., and Ren, G., "Design and Implementation of FPGA-Based FSK IF Digital Receiver", 1st International Symposium on Systems and Control in Aerospace and Astronautics (ISSCAA), 819 - 821, January 2006.

[5] Andraka, Ray, "A survey of CORDIC algorithm for FPGA based computers", Proceedings of the 1998 ACM/SIGDA Sixth International Symposium on Field Programmable Gate Arrays, 191 - 200, Feb. 22-24, 1998.

[6] Volder, Jack E., "The CORDIC Trigonometric Computing Technique", IRE Transactions on Electronic Computers, Volume EC-8, 330 - 334, September 1959.